# Power Quality Improvement of a Grid through Dual Voltage Source Inverter

<sup>1</sup>K. Mohanapreethi, <sup>2</sup>T. Ravi Kumar, <sup>3</sup>TNVLN Kumar <sup>1</sup>PG scholar of EEE, <sup>2</sup>Associate Professor of EEE Dept., <sup>3</sup>Head of the department of EEE <sup>1,2,3</sup> Geethanjali Institute of Science and Technology, affiliated to JNTUA, Gangavaram, SPSR Nellore.

**Abstract** — The venture introduces a double voltage source inverter (DVSI) plan to improve dependability and power nature of the smaller scale lattice framework. The proposed plan is incorporated two inverters, which enables the miniaturized scale matrix to trade control delivered by the appropriated vitality assets (DERs) moreover to reimburse the adjacent nonlinear and uneven load. The control calculations are made in light of immediate symmetrical part hypothesis (ISCT) to work DVSI in framework sharing and lattice implanting modes. The proposed scheme has extended immovable quality, cut down data transfer capacity essential of the essential inverter, cut down cost on account of diminishing in channel size, and better utilization of miniaturized scale lattice control while using reduced dc-interface voltage rating for the key inverter. These segments make the DVSI plot a promising option for miniaturized scale framework providing sensitive weights. The topology and control estimation are endorsed through expansive reenactment and test comes to fruition.

#### I. INTRODUCTION

Innovative advance and ecological concerns drive the power framework to an outlook change with more renewable vitality sources incorporated to the system by method for appropriated era (DG). These DG units with made control out of close-by era and storerooms outline a smaller scale lattice [1]. A lattice intuitive inverter assumes a vital part in trading power from the miniaturized scale framework to the network and the associated stack [2], [3]. This small scale framework inverter can either work in a lattice sharing mode while providing a bit of neighborhood load or in matrix infusing mode, by infusing energy to the key network. The essential focus of this work is to recognize twofold

The essential focus of this work is to recognize twofold functionalities in an inverter that would give the dynamic power infusion from a sun based PV structure besides acts as a dynamic power channel, remunerating unbalances and the receptive power vital for different burdens associated with the framework.

A dispersion static compensator (DSTATCOM) is utilized for voltage heading besides for dynamic power

infusion. The control plot keeps up the power adjust at the lattice terminal amid the wind varieties utilizing sliding mode control. This venture displays a double voltage source inverter (DVSI) scheme, in which the power made by the smaller scale lattice is imbued as genuine power by the fundamental voltage source inverter (MVSI) and the consonant, receptive and unequal load remuneration is performed by assistant voltage source inverter (AVSI). This has slack that the evaluated limit of MVSI can basically be used to implant genuine energy to the lattice, if satisfactory renewable power is available at the dc interface. In the DVSI plot, as total load power is given by two inverters, control misfortunes over the semiconductor switches of each inverter are decreased. This fabricates its unflinching quality when diverged from a lone inverter with multifunctional limits [13].

In like manner, more diminutive size measured inverters can work at high trading frequencies with a reduced size of interfacing inductor; the channel cost gets diminished [14]. Also, as the principle inverter is giving genuine power, the inverter needs to track the significant positive progression of current. This lessens the data transmission essential of the primary inverter. The inverters in the proposed contrive use two separate dc joins. Since the helper inverter is giving zero grouping of load current, a three-organize three-leg inverter topology with a singular dc stockpiling capacitor can be used for the principle inverter.

This subsequently diminishes the dc-interface voltage need of the fundamental inverter. Subsequently, the use of two separate inverters in the proposed DVSI contrive gives extended reliability, better utilization of small scale matrix control, reduced dc framework voltage rating, less data transfer capacity essential of the primary inverter, and decreased channel appraise [13]. Control calculations are created by quick symmetrical part hypothesis (ISCT) to work DVSI in network related mode, while considering non firm lattice voltage [15], [16]. The extraction of essential positive arrangement of PCC voltage is done by dq0 change [17]. The control strategy is attempted with two parallel inverters connected with a three-stage four-wire dissemination framework. Ampleness of the proposed control

calculation is affirmed through organized recreation and exploratory results.

#### II. DUAL VOLTAGE SOURCE INVERTER

#### A. System Topology

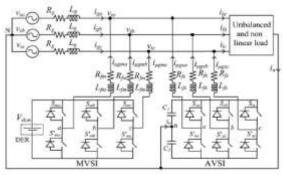

The anticipated DVSI topology is showed up in Fig. 1. It involves a nuetral point cut (NPC) inverter to acknowledge AVSI and a three-leg inverter for MVSI [18]. These are connected with network at the PCC and giving a nonlinear and unbalanced load. The limit of the AVSI is to reimburse the music, receptive and unbalance fragments in load streams. Here, load streams in three stages are spoken to by  $i_{la}$ ,  $i_{lb}$ , and  $i_{lc}$ , individually. Additionally,  $i_{g(abc)}$ ,  $i_{\mu g \, m(abc)}$ , and  $i_{\mu g \, x(abc)}$  show framework streams, MVSI ebbs and flows, and AVSI ebbs and flows in three stages, independently. The dc connection of the AVSI utilizes a split capacitor topology, with two capacitors C1 and C2. The MVSI passes on the open power at appropriated vitality asset (DER) to lattice.

The DER can be a dc source or an air conditioner source with rectifier coupled to dc connect. Ordinarily, renewable vitality sources like energy component and PV make control at variable low dc voltage, while the variable speed wind turbines deliver control at variable air conditioning voltage. In this way, the power created from these sources use a power shaping stage before it is connected with the commitment of MVSI. In this study, DER is being addressed as a dc source. An inductor channel is used to evacuate the high-recurrence exchanging segments created due to the trading of force electronic switches in the inverters [19]. The framework considered in this study is relied upon to have some measure of feeder resistance Rg and inductance Lg. Because of the nearness of this feeder impedance, PCC voltage is influenced with harmonics [20].

Fig. 1. Topology of proposed DVSI scheme.

#### B. Design of DVSI Parameters

1) **AVSI**: The important parameters of AVSI like dc-link voltage  $(V_{dc})$ , dc storage capacitors  $(C_1$  and  $C_2)$ , interfacing inductance  $(L_{fx})$ , and hysteresis band  $(\pm h_x)$  are chosen in view of the plan strategy for split capacitor

DSTATCOM topology [16]. The dc-link voltage over every capacitor is taken as 1.6 times the peak of phase voltage. The aggregate dc-link voltage reference ( $V_{dcref}$ ) is found to be 1040 V.

Estimations of dc capacitors of AVSI are picked in view of the adjustment in dc-link voltage amid drifters. Let add up to load rating is S kVA. In the most pessimistic scenario, the heap power may shift from least to greatest, i.e., from 0 to S kVA. AVSI requirements to trade real power amid transient to maintain the heap power request. This exchange of real power amid the transient will bring about deviation of capacitor voltage from its reference esteem. Accept that the voltage controller takes n cycles, i.e.,  $_{\rm nT}$  seconds to act, where T is the system era. Henceforth, most extreme energy trade by AVSI amid transient will be nST. This energy will be equivalent to change in the capacitor put away energy. Hence

$$\frac{1}{2}C_1(V_{der}^2 - V_{de1}^2) = nST \tag{1}$$

where  $V_{\rm dcr}$  and  $V_{\rm dcl}$  are the reference dc voltage and most extraordinary permissible dc voltage across over C1 in the midst of transient, individually. Here, S=5 kVA,  $V_{\rm dcr}=520$  V,  $V_{\rm dcl}=0.8*V_{\rm dcr}$  or  $1.2*V_{\rm dcr}, n=1$ , and T=0.02 s. Substituting these values in (1), the dc link capacitance ( $C_1$ ) is calculated to be 2000  $\mu$ F. Equal charge of capacitance is selected for  $C_2$ . The interfacing inductance is given by

$$L_{fx} = \frac{1.6 \, V_m}{4 \, h_x f_{\text{max}}}.\tag{2}$$

Expecting a most extreme switching frequency ( $f_{max}$ ) of 10 kHz and hysteresis band ( $h_x$ ) as 5% of load current (0.5 A), the estimation of  $L_{fx}$  is figured to be 26 mH.

2) MVSI: The MVSI uses a three-leg inverter topology. Its dc-link voltage is obtained as  $1.15 * V_{ml}$ , where  $V_{ml}$  is the pinnacle estimation of line voltage. This is ascertained to be 648 V. Additionally, MVSI supplies an adjusted sinusoidal current at solidarity control figure. In this way, zero arrangement exchanging music will be missing in the yield current of MVSI. This lessens the channel necessity for MVSI when contrasted with AVSI [21]. In this examination, a channel inductance ( $L_{fin}$ ) of 5 mH is used.

# II. CONTROL STRATEGY FOR DVSI SCHEME

#### A. Fundamental Voltage Extraction

The control estimation for reference current era using ISCT requires balanced sinusoidal PCC voltages. As a

result of the nearness of feeder impedance, PCC voltages are contorted. In this way, the principal positive arrangement segments of the PCC voltages are extricated for the reference current era. To change over the mutilated PCC voltages to adjusted

Fig. 2. Schematic diagram of PLL.

sinus oidal voltages, dq0 transformation is used. The PCC voltages in natural reference frame ( $v_{ta}$ ,  $v_{tb}$ , and  $v_{tc}$ ) are first transformed into dq0 reference frame as given by

$$\begin{bmatrix} v_{td} \\ v_{tq} \\ v_{t0} \end{bmatrix} = C \begin{bmatrix} v_{ta} \\ v_{tb} \\ v_{tc} \end{bmatrix}$$

(3)

where

$$C = \sqrt{\frac{2}{3}} \begin{bmatrix} \sin\theta & \sin(\theta - \frac{2\pi}{3}) & \sin(\theta + \frac{2\pi}{3}) \\ \cos\theta & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}.$$

In order to get  $\theta$ , a modified synchronous reference frame (SRF) phase locked loop (PLL) is used. The schematic diagram of this PLL is shown in Fig. 2. It mainly consists of a proportional integral (PI) controller and an integrator. In this PLL, the SRF terminal voltage in q-axis  $(v_{tq})$  is compared with 0 V and the error voltage thus obtained is given to the PI controller. The frequency deviation  $\Delta \omega$  is then added to the reference frequency  $\omega 0$  and finally given to the integrator to get  $\theta$ . It can be proved that, when,  $\theta = \omega 0 t$  and by using the Park's transformation matrix (C), q-axis voltage in dq0 frame becomes zero and hence the PLL will be locked to the reference frequency  $(\omega 0)$ . As PCC voltages are distorted, the transformed voltages in dq0 frame ( $v_{td}$  and  $v_{tq}$ ) contain average and oscillating components of voltages. These can be represented as

$$v_{td} = \overline{v}_{td} + \widetilde{v}_{td}, \quad v_{tq} = \overline{v}_{tq} + \widetilde{v}_{tq}$$

(4)

Where  $\tilde{v}_{td}$  and  $\tilde{v}_{tq}$  represent the average components of  $v_{td}$  and, respectively. The terms  $\tilde{v}_{td}$  and  $\tilde{v}_{tq}$  indicate the oscillating components of  $v_{td}$  and  $v_{tq}$  respectively. Now the fundamental positive sequence of PCC voltages in natural reference frame can be obtained with the help of inverse dq0 transformation as given by

$$\begin{bmatrix} v_{ta1}^+ \\ v_{tb1}^+ \\ v_{tq}^+ \end{bmatrix} = C^T \begin{bmatrix} \overline{v}_{td} \\ \overline{v}_{tq} \\ 0 \end{bmatrix}. \tag{5}$$

These voltages  $v_{ta1}^+$ ,  $v_{tb1}^+$ , and  $v_{tc1}^+$  are used in the reference current generation algorithms, so as to draw balanced sinusoidal currents from the grid.

#### **B.** Control Strategy of DVSI

Control strategy of DVSI is developed in such a way that grid and MVSI together share the active load power, and AVSI supplies rest of the power components demanded by the load.

## 1. Reference Current Generation for Auxiliary Inverter:

The dc-link voltage of the AVSI should be maintained constant for proper operation of the auxiliary inverter. DC-link voltage variation occurs in auxiliary inverter due to its switching and ohmic losses. These losses termed as  $P_{loss}$  should also be supplied by the grid. An expression for  $P_{loss}$  is determined on the condition that normal dc capacitor current is zero to keep up a steady capacitor voltage [15]. The deviation of normal capacitor current from zero will reflect as an adjustment in capacitor voltage from a relentless state esteem. A PI controller is used to generate  $P_{loss}$  term as given by

$$P_{\text{loss}} = K_{Pv} e_{v\text{dc}} + K_{Iv} \int e_{v\text{dc}} dt$$

(13)

where  $e_{vdc} = V_{dcref} - v_{dc}$ ,  $v_{dc}$  represents the actual voltage sensed and updated once in a cycle. In the above equation,  $K_{Pv}$  and  $K_{Iv}$  represent the proportional and integral gains of dc-link PI controller, respectively. The  $P_{loss}$  term in this manner acquired ought to be provided by the framework, and in this manner AVSI reference streams can be gotten as given in (14). Here, the dc-connect voltage PI controller increases are chosen in order to guarantee security and better element reaction amid

$$i_{\mu gxa}^* = i_{la} - \left(\frac{v_{ta1}^+}{\sum_{j=a,b,c} v_{tj}^{+2}}\right) (P_l + P_{loss})$$

$i_{\mu gxb}^* = i_{lb} - \left(\frac{v_{tb1}^+}{\sum_{j=a,b,c} v_{tj}^{+2}}\right) (P_l + P_{loss})$

$i_{\mu gxc}^* = i_{lc} - \left(\frac{v_{tc1}^+}{\sum_{j=a,b,c} v_{tj}^{+2}}\right) (P_l + P_{loss}).$

(14)

#### 2. Reference Current Generation for Main Inverter:

The MVSI supplies adjusted sinusoidal streams in view of the accessible renewable power at DER. On the off chance that MVSI misfortunes are dismissed, the influence infused to framework will be equivalent to that accessible at DER ( $P_{\mu g}$ ). The following equation, which

is derived from ISCT can be used to generate MVSI reference currents for three phases (a, b, and c)

$$\sharp_{\mu gm(abc)}^* = \left(\frac{v_{t(abc)1}^+}{\sum_{j=a,b,c} v_{tj}^{+2}}\right) P_{\mu g} \tag{15}$$

where  $P_{\mu g}$  is the available power at the dc link of MVSI.

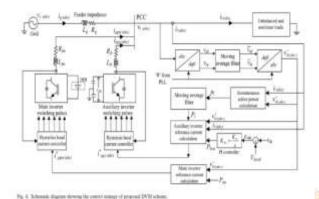

Fig. 4. Schematic diagram showing the control strategy of proposed DVSI scheme.

The reference streams acquired from (14) to (15) are followed by utilizing hysteresis band current controller (HBCC). HBCC plans depend on an input circle, as a rule with a two-level comparator. This controller has the benefit of pinnacle current restricting limit, great element reaction, and effortlessness in usage [14]. A hysteresis controller is a high-increase relative controller. This controller includes certain stage slack in the operation in view of the hysteresis band and won't make the framework unsteady. Additionally, the proposed DVSI plot utilizes a first-arrange inductor channel which holds the shut circle framework dependability. The whole control technique schematically spoken to in Fig. 4. Applying Kirchoff's present law (KCL) at the PCC in Fig. 4

$$i_{\mu ax j} = i_{l j} - (i_{q j} + i_{\mu am j}), \text{ for } j = a, b, c.$$

(16)

By using (14) and (16), an expression for reference grid current in phase- $a(i_{qa}^*)$  can be obtained as

$$i_{ga}^* = \left(\frac{v_{ta1}^+}{\sum_{l=a,b,c} v_{tj}^{+2}}\right) [(P_l + P_{loss}) - P_{\mu g}],$$

(17)

It can be observed that, if the quantity  $(P_l + P_{loss})$  is greater than  $P_{\mu g}$ , the term[ $(P_l + P_{loss}) - P_{\mu g}$ ] will be a positive quantity, and  $i^*_{ga}$  will be in phase with  $v^+_{ta1}$ . This operation can be called as the matrix supporting or network sharing mode, as the aggregate load control request is shared between the principle inverter and the

lattice. The term, $P_{loss}$  is usually very small compared to Pl. On the other hand, if  $(P_l + P_{loss})$  is less than  $P_{\mu g}$ , then  $[(P_l + P_{loss}) - P_{\mu g}]$  will be a negative quantity, and hence  $i^*$  will be in phase opposition with  $v^+_{ta1}$ . This method of operation is known as the framework infusing mode, as the abundance power is infused to network.

#### IV. SIMULATION RESULTS

The recreation model of DVSI plan appeared in Fig. 1 is created in PSCAD 4.2.1 to assess the execution. The reenactment parameters of the framework are given in Table I. The reproduction concentrate on shows the network sharing and lattice infusing methods of operation of DVSI plan in relentless state and additionally in transient conditions.

TABLE I

System Parameters For Simulation Study

| Parameters                  | Values                                                                                                                                                                                                      |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Grid voltage                | 400 V(L-L)                                                                                                                                                                                                  |

| Fundamental frequency       | 50 Hz                                                                                                                                                                                                       |

| Feeder impedance            | $R_{\alpha} = 0.5 \Omega$ , $L_{\alpha} = 1.0 \text{ mH}$                                                                                                                                                   |

| AVSI                        | $C_1 = C_2 = 2000 \mu\text{F}$<br>$V_{deref} = 1040 \text{V}$<br>Interfacing inductor, $L_{fx} = 20 \text{mH}$<br>Inductor resistance, $R_{fx} = 0.25 \Omega$<br>Hysteresis band $(\pm h_x) = 0.1 \text{A}$ |

| MVSI                        | DC-link voltage, $V_{dem} = 650 \text{ V}$<br>Interfacing inductor, $L_{fm} = 5 \text{ mH}$<br>Inductor resistance, $R_{fm} = 0.25 \Omega$<br>Hysteresis band $(\pm h_m) = 0.1 \text{ A}$                   |

| Unbalanced linear load      | $Z_{la} = 35 + j19 \Omega$<br>$Z_{lb} = 30 + j15 \Omega$<br>$Z_{lc} = 23 + j12 \Omega$                                                                                                                      |

| Nonlinear load              | 3 φ diode bridge rectifier<br>with DC side current of 3.0 A                                                                                                                                                 |

| DC voltage controller gains | $K_{Pv} = 10$ , $K_{Iv} = 0.05$                                                                                                                                                                             |

Fig.5: DER voltage

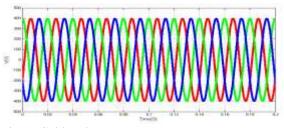

Fig.6: Grid voltage:

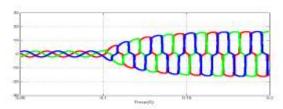

Fig.7: MVSI current

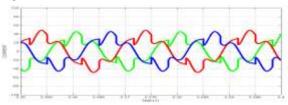

Fig.8: AVSI current

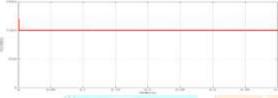

Fig.9: AVSI Voltage

Fig. 10: Load voltage

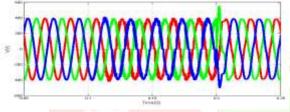

Fig.11: Load Current

#### VI. CONCLUSION

A DVSI plan is proposed for microgrid frameworks with upgraded control quality. Control calculations are produced to create reference streams for DVSI utilizing ISCT. The proposed conspire has the capacity to trade control from dispersed generators (DGs) furthermore to repay the nearby unequal and nonlinear load. The execution of the proposed conspire has been approved through reproduction and exploratory studies. When contrasted with a solitary inverter with multifunctional abilities, a DVSI has numerous preferences, for example, expanded dependability, bring down cost because of the diminishment in channel size, and more usage of inverter ability to infuse genuine power from

DGs to microgrid. Also, the utilization of three-stage, threewire topology for the primary inverter lessens the dc-connect voltage prerequisite. Along these lines, a DVSI plan is an appropriate interfacing choice for microgrid providing delicate burdens.

#### **SCREEN SHOT:**

#### MATLAB:

Simulink library browser:

Block diagram:

## DER Voltage:

Grid Voltage:

MVSI current:

AVSI Current:

AVSI Voltage:

Load voltage:

#### Load current:

PCC I:

PCC V& I:

#### Voltage magnitude:

### Current magnitude:

#### REFERENCES

- [1] A. Kahrobaeian and Y.-R. Mohamed, "Interactive distributed generation interface for flexible micro-grid operation in smart distribution systems," IEEE Trans. Sustain. Energy, vol. 3, no. 2, pp. 295–305, Apr. 2012.

- [2] N. R. Tummuru, M. K. Mishra, and S. Srinivas, "Multifunctional VSC controlled microgrid using instantaneous symmetrical components theory," IEEE Trans. Sustain. Energy, vol. 5, no. 1, pp. 313–322, Jan. 2014.

- [3] Y. Zhang, N. Gatsis, and G. Giannakis, "Robust energy management for microgrids with high-penetration renewables," IEEE Trans. Sustain. Energy, vol. 4, no. 4, pp. 944–953, Oct. 2013.

- [4] R. Majumder, A. Ghosh, G. Ledwich, and F. Zare, "Load sharing and power quality enhanced operation of

- a distributed microgrid," IET Renewable Power Gener., vol. 3, no. 2, pp. 109–119, Jun. 2009.

- [5] J. Guerrero, P. C. Loh, T.-L. Lee, and M. Chandorkar, "Advanced control architectures for intelligent microgrids—Part II: Power quality, energy storage, and ac/dc microgrids," IEEE Trans. Ind. Electron., vol. 60, no. 4, pp. 1263–1270, Dec. 2013.

- [6] Y. Li, D. Vilathgamuwa, and P. C. Loh, "Microgrid power quality enhancement using a three-phase four-wire grid-interfacing compensator," IEEE Trans. Ind. Appl., vol. 41, no. 6, pp. 1707–1719, Nov. 2005.

- [7] M. Schonardie, R. Coelho, R. Schweitzer, and D. Martins, "Control of the active and reactive power using dq0 transformation in a three-phase grid-connected PV system," in Proc. IEEE Int. Symp. Ind. Electron., May 2012, pp. 264–269.

- [8] R. S. Bajpai and R. Gupta, "Voltage and power flow control of grid connected wind generation system using DSTATCOM," in Proc. IEEE Power Energy Soc. Gen. Meeting—Convers. Del. Elect. Energy 21<sup>st</sup> Century, Jul. 2008, pp. 1–6.

- [9] M. Singh, V. Khadkikar, A. Chandra, and R. Varma, "Grid interconnection of renewable energy sources at the distribution level with power-quality improvement features," IEEE Trans. Power Del., vol. 26, no. 1, pp. 307–315, Jan. 2011.

- [10] H.-G. Yeh, D. Gayme, and S. Low, "Adaptive VAR control for distribution circuits with photovoltaic generators," IEEE Trans. Power Syst., vol. 27, no. 3, pp. 1656–1663, Aug. 2012.

- [11] C. Demoulias, "A new simple analytical method for calculating the optimum inverter size in grid-connected PV plants," Electr. Power Syst. Res., vol. 80, no. 10, pp. 1197–1204, 2010.

- [12] R. Tonkoski, D. Turcotte, and T. H. M. EL-Fouly, "Impact of high PV penetration on voltage profiles in residential neighborhoods," IEEE Trans. Sustain. Energy, vol. 3, no. 3, pp. 518–527, Jul. 2012.

- [13] X. Yu and A. Khambadkone, "Reliability analysis and cost optimization of parallel-inverter system," IEEE Trans. Ind. Electron., vol. 59, no. 10, pp. 3881–3889, Oct. 2012.

- [14] M. K. Mishra and K. Karthikeyan, "Design and analysis of voltage source inverter for active compensators to compensate unbalanced and nonlinear loads," in Proc. IEEE Int. Power Eng. Conf., 2007, pp. 649–654.

- [15] A. Ghosh and A. Joshi, "A new approach to load balancing and power factor correction in power distribution system," IEEE Trans. Power Del., vol. 15, no. 1, pp. 417–422, Jan. 2000.

- [16] U. Rao, M. K. Mishra, and A. Ghosh, "Control strategies for load compensation using instantaneous symmetrical component theory under different supply

- voltages," IEEE Trans. Power Del., vol. 23, no. 4, pp. 2310–2317, Oct. 2008.

- [17] P. Rodriguez et al., "A stationary reference frame grid synchronization system for three-phase grid-connected power converters under adverse grid conditions," IEEE Trans. Power Electron., vol. 27, no. 1, pp. 99–112, Jan. 2012.

- [18] S. Iyer, A. Ghosh, and A. Joshi, "Inverter topologies for DSTATCOM applications—A simulation study," Electr. Power Syst. Res., vol. 75, no. 23, pp. 161–170, 2005.

- [19] Y. Tang, P. C. Loh, P. Wang, F. H. Choo, and F. Gao, "Exploring inherent damping characteristic of LCL filters for three-phase grid-connected voltage source inverters," IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1433–1443, Mar. 2012.

- [20] D. Vilathgamuwa, P. C. Loh, and Y. Li, "Protection of microgrids during utility voltage sags," IEEE Trans. Ind. Electron., vol. 53, no. 5,

- pp. 1427-1436, Oct. 2006.

- [21] M. Prodanovic and T. Green, "Control and filter design of three-phase inverters for high power quality grid connection," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 373–380, Jan. 2003.

- [22] M. Hamid, A. Jusoh, and M. Anwari, "Photovoltaic plant with reduced output current harmonics using generation-side active power conditioner," IET Renewable Power Gener., vol. 8, no. 7, pp. 817–826, Sep. 2014.

#### **Author's Profile**

**K.** Mohanapreethi received her B.Tech degree in Electrical and Electronics Engineering from SKR College of Engineering and technology, A.P. she is currently pursuing M.Tech in Power Electronics Engineering from Geethanjali

Institute of Science and Technology, Gangavaram SPSR Nellore(dist), affiliated to JNTUA.

**T. Ravi Kumar** received Bachelor of Technology degree in Electrical & Electronics Engineering from Narayana engineering college Nellore, JNTUH and Master,s degree from JNTU college of

Engineering, Anantapur . Currently, pursuing Ph.D in KL University and working as an Associate Professor in Geethanjali Institute Of Science & Technology, Nellore, JNTU Anantapur, A.P. He is having 11 years of teaching experience .His areas of interests in Power systems and Power Electronic & Drives. His research interests

include electric machines, machine drives, power electronics/conversion, and practical use and improvement of modern control and estimation theory in electric machine drives and power electronics control.

**Mr. TNVLN Kumar** M. Tech, PhD is currently working as Professor & Head of the EEE Department at Geethanjali Institute of Science Technology, Nellore, A.P. India.